# NOVEL CHIP GEOMETRIES FOR THz SCHOTTKY DIODES

W. M. Kelly, Farran Technology Ltd., Cork, IrelandS. Mackenzie and P. Maaskant, National Microelectronics Research Centre, University College, Cork, Ireland

#### Introduction

For THz applications involving low noise heterodyne receivers, the whiskercontacted Schottky barrier diode provides excellent room temperature and cryogenic performance. The traditional chip structure consists of a honeycomb anode array on top of a chip which is typically  $100\mu$ m square and  $100\mu$ m thick, with ohmic contacts on the back, or occasionally on the side, so-called notch-front chips [1]. The chip is mounted in a variety of structures such as across waveguides, on planar filter metallisations, or at the end of coaxial filters, and the ideal chip shape for these differs. It is important to build the chip structure into the electrical design, especially at short wavelengths where chip dimensions are comparable to waveguide dimensions.

### **Fabrication Options**

In light of the above, we explore in this paper the possibilities for fabricating new or improved chip structures using advanced processing techniques such as reactive ion etching (RIE), etch-stop layers, epitaxial lift-off (ELO), and bonding by atomic rearrangement (BAR). RIE enables the etching of deep features (up to hundreds of micrometers) into the surface of the semiconductor wafer [2]. Additionally, the side profiles of the etched features can be controlled, varying between purely isotropic to highly anisotropic. Etch-stop-layers are often used to enable accurate control of vertical etching. ELO is a technique involving the use of chemical etching and often etch-stop-layers, in which the surface layers including the active devices are lifted off one substrate and transferred to another [3]. For example, active optoelectronic devices can be fabricated on InP or GaAs substrates and transferred to Si wafers where they can be interconnected with electronic circuitry [4]. In respect to millimetre wave devices, it can be envisaged as a good technique for producing very thin planar chips. BAR [5] is an alternative for achieving this result, in which pieces of one semiconductor can be

Page 405

attached to another using a high temperature controlled environment anneal to create the bond. These various techniques enable processes to be developed for the fabrication of chips with arbitrary cross-sectional shape with high yield and with little if any limitation on the electrical characteristics of the anode junction.

#### **Fabrication Process**

The most straightforward technological solution involves RIE. We have developed a process which allows diode chips of circular, square or rectangular crosssection to be fabricated in thicknesses down to about 20 $\mu$ m. The process commences by the deposition of a layer of passivation, usually SiO<sub>2</sub>, to a thickness of about 0.5 $\mu$ m. This is followed by the lithography for the anode definition. We use an electron beam lithographic system along with dry-developable sylilated resist technology for this step. The anode holes are defined in the SiO<sub>2</sub> layer using RIE with CHF<sub>3</sub>/Ar gas. The chip shape is then defined by a second level of lithography, 30 $\mu$ m circles in the case of the chips described here, followed by deep RIE in SiCl<sub>4</sub> gas. An ohmic contact is electroplated on to the mesa sidewalls and alloyed prior to Pt/Au anode metallisation. The substrate is removed by a chemical/grinding process and a back contact metallisation is evaporated on to the chips before separation for electrical characterisation.

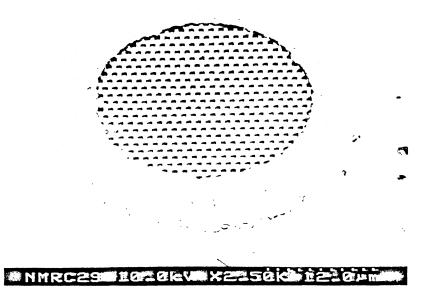

Figure 1. Micrograph of 30µm diameter cylindrical Schottky diode chip. The chip is 30µm high and is patterned with 0.9µm anodes.

The micrograph in figure 1 shows for example a single  $30\mu m$  diameter by  $30\mu m$  high cylindrical diode chip with an array of micron-sized Schottky anodes on the top surface. This chip is ideally shaped for location at the end of a coaxial RF choke filter.

#### **Device Characteristics**

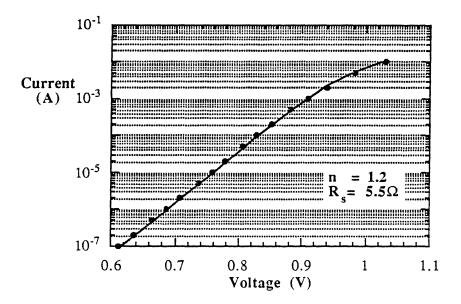

The above procedure has been used to fabricate a batch of demonstrator cylindrical diode chips with anode diameter of  $1.3\mu m$  on MOVPE grown GaAs. This material had a 5 $\mu$ m buffer layer of doping  $4\times10^{18}$  cm<sup>-3</sup>, with a 600Å epilayer doped to  $5\times10^{17}$  cm<sup>-3</sup>. DC electrical characteristics of a typical diode are shown in figure 2. The data is presented as a plot of log(I) against V, together with a curve of I =  $I_0 \exp(q(V-IR_s)/\eta kT)$ . The series resistance of the device has been measured as  $R_s = 5.5\Omega$  at a current of 10mA, consistent with the expected epilayer resistance and ohmic contact area. The diodes exhibit an ideality factor of  $\eta = 1.2$  and a zero-bias junction capacitance of 6fF. Thus it can be seen that this new process can be used for the fabrication of smaller chip geometries without adversely affecting the electrical characteristics of the resulting devices.

Figure 2. I-V characteristic of 1.3µm diameter diode on cylindrical chip

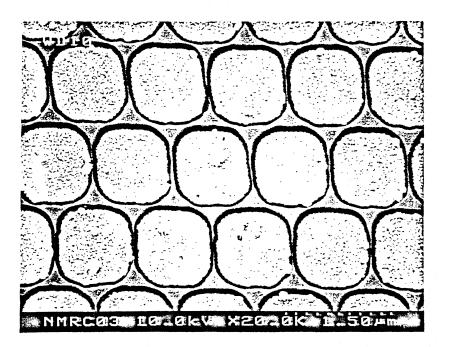

We have also made devices with square anodes and high packing density as in figure 3, allowing for easy whisker contacting.

Figure 3. Densely packed 0.9µm square anodes with Pt/Au metallisation

# Conclusions

An advanced process for the fabrication of new Schottky barrier diode chip geometries has been developed. The technique facilitates the production of chips with arbitrary cross-section and is especially suited to the fabrication of chips with dimensions less than the  $80\mu$ m limit allowed by dicing. The devices are mechanically robust and exhibit no adverse effects on their electrical characteristics as a result of the fabrication procedure. Using this process, the structure of the diode chip can be matched to that of the circuit components, representing a significant advance for optimising the performance of submillimetre systems incorporating Schottky diode technology.

# Acknowledgements

The authors would like to thank the EU Environmental Programme Contract No. EV5V-CT92-0081 for part support of this work.

# References

- 1. Verlangieri P.A. and Schneider M.V., Intl. J. Infrared and Millimeter Waves, Vol.6, No. 12, pp 1191-1202, 1985

- 2. Gorowitz B. and Saia R.J., in VLSI Electronics Microstructure Series, Vol.8, Einspruch N.G. and Brown D.M., Eds., Academic Press Inc, San Diego, 1984

- Chan W.K., Yi-Yan A. and Gmitter T.J., IEEE J. Quant. Electron., Vol. 27, No. 3, pp 717-725, 1991

- Ersen A., Schnitzer I., Yablonovitch E. and Gmitter T., Solid State Electron., Vol. 36, No. 12, pp 1721-1739, 1993

- 5. Liau Z.L. and Mull D.E., Appl. Phys. Lett., Vol. 56, No. 8, pp 737-739, 1990