## Frequency conversion to 368 GHz Using Resonant Tunneling Diodes

## O. Tanguy\*, D. Lippens\*, J. Bruston\*\*, J.C. Pernot\*\*, G. Beaudin\*\* J. Nagle\*\*\* and B. Vinter\*\*\*

Abstract: We report on measurements of quantum-well heterostructures diodes at millimeter and submillimeter wavelengths. The samples were fabricated from high quality strained layer epitaxies with design rules suitable for their characterisation at very high frequencies. The devices with barrier thicknesses ranging from 1.1nm to 1.7nm exhibit excellent dc characteristics with peak-to-valley current ratios up to 7:1 and peak current densities between 50 and 150 kA/cm<sup>2</sup>. These structures have been mounted in a tripler cross-waveguide fixture and rf tested by measuring their impedance at millimeter-wavelengths and by investigating their rf properties in a frequency converter experiment. Harmonic multiplication to a frequency of 368 GHz with an output power of  $0.8\mu$ W was achieved. These results are interpreted on the basis of non linear harmonic balance simulation codes which give some guidelines for optimizing the devices in terms of structures and operating conditions.

Introduction: Resonant tunneling diodes based on the resonant tunneling effect in double barrier heterostructures(DBH) are among the most promising solid state candidates for operating at very high frequencies due to the very short time response of the physical mechanisms involved. They exhibit strong negative differential conductance effects in their current-voltage characteristics so they can be used in non linear high speed applications such as oscillators<sup>[1]</sup> and frequency harmonic multipliers<sup>[2]</sup>. For these RTD-based analogue applications, one of the most important issue is the behaviour of the conductance not only as a function of voltage, defining by this means the resistive non linearity, but also as a function of frequency. This is particularly true in the context of the remarkable advancement in the crystal growth which makes now possible to grow ultra thin layers with atomically sharp interfaces, increasing by this means the frequency capability of devices. In this paper, we report on measurements carried out on such high performance diodes which have been successfully fabricated from strained-layer epitaxies. The frequency evaluation of samples has been carried out mainly in a frequency converter experiment starting from a 123 GHz input frequency and by tripling this fundamental oscillation for an output at 368GHz.

Design and fabrication: Figure 1 shows the new structure that we used for the design. For harmonic multiplier applications, it is imperative to optimize the current voltage characteristics to achieve high speed operation and simultaneously pronounced variations of the conductance in order to maximize the harmonic content. To achieve high frequency operation, we need to optimize the peak current density and the peak-to-valley current ratio which are the key parameters in the present application. Also, a decrease in the peak voltage can reduce the amount of power to pump the diode. To this aim, we used a double barrier in a triple-well configuration. In short, this layer is designed with local InGaAs potential perturbations forming buried wells on each side and within the DBH. By this means we take advantage of a lower effective mass with the associated benefit of a higher discontinuity at the heterointerfaces. Also, a decrease in the peak voltage can be expected because the quantum level of the DBH is lowered with respect to the emitter reference energy. The wells are filled up as a consequence of the charge transfer from the adjacent layers leading to the formation of dipoles as in any modulation doped structure. The first step in the design was thus to determine carefully the charges trapped in the wells and the escape times through the barriers. To deal with this issue, a self consistent numerical procedure was used with the potential profile reported in Figure 1. The calculation of eigenstates and of their lifetimes permits one to deduce

peak current densities and peak-to-valley current ratios<sup>[3]</sup>.

Epilayers were fabricated by Molecular Beam Epitaxy starting from a GaAs semi insulating substrate. The growth sequence is given in Figure 2. The ultra thin barriers of AlAs with thicknesses between 1.1 nm and 1.7 nm allow us to achieve a relatively high tunneling transmission. The prewell and postwell are 5nm thick whereas the midwell is 4nm thick. We have intentionally limited the Indium content of InGaAs layers to 0.1 in order to avoid misfit dislocations. For each transition a 0.5nm thick GaAs spacer was systematically placed to recover good surface states. The triple well double barrier zone is then sandwiched between two 500nm thick n+ GaAs layers acting as electron reservoirs followed by 10nm thick cladding layers doped  $10^{17}$  cm<sup>-3</sup>. Before each series of tunneling wafers, a calibration was made to determine InGaAs and AlAs growth rates so that the layer thicknesses can be controlled accurately.

| GaAs          | 3 1018 cm-J  | 500 nm        |

|---------------|--------------|---------------|

| GaAs          | 1 1017 cm-J  | 10 nm         |

| GaAs          | Undoped (UD) | 5 nm          |

| Ing Gagens    | UD           | ភ្ n <b>m</b> |

| GaAs          | UD           | 0.5 nm        |

| ALAs          | ា            | 1.7 nm        |

| GaAs          | συ           | 0.5 nm        |

| Ing 1 Gan sAs | ۵U           | 4 am          |

| GaAs          | מט           | 0.5 nm        |

| AlAs          | συ           | 1.7 nm        |

| GaAs          | UD           | 0.3 nm        |

| Inn I Gangas  | au           | ភ័ nm         |

| Gaas          | UD           | 5 nm          |

| GaAs          | 1 1017 cm-J  | 10 nm         |

| Gaas          | 3 1018 cm-3  | 500 nm        |

|               | SI Substrate |               |

## Fig. 1 Design of a Double Barrier Heterostructure in a triple well configuration

Fig. 2 Growth sequence

Devices were fabricated in a mesa-etched technology including patterning of  $4\mu$ mdiameter dots on the epitaxial side of the wafer, deposition of AuGeNi metallization and alloying of these layers to make ohmic contacts. In order to avoid undercutting effects which are source of trouble in chemical etching, mesa isolation was performed with chlorine ion beam assisted etching (R.I.E.) using the patterned metal as a mask. Pillars with well-defined sidewalls have thus been successfully fabricated. Figure 3 gives a scanning electron micrograph of a representative device. In view of rf testing some of the samples have also been thinned down to 100 $\mu$ m followed by a uniform deposition of material contact and alloying. Lastly, the wafer have been diced into chips of 100 $\mu$ m -side to be whisker-contacted in a rf test fixture.

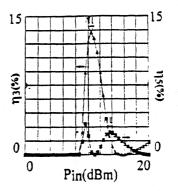

An HP dc set-up was used for measuring the current voltage characteristics of the diodes and to calculate the small signal conductance of the samples from the derivative of the I-V curve at each bias point. Figure 4 gives an example of current voltage characteristics we obtained at room temperature. In the NDC region abrupt changes in G are apparent due to the well known shoulder-like I-V resulting from spurious low frequency self-oscillations. Also note the very good symmetry of the forward and reverse characteristics which reveals the quality of samples. For the three technological runs with barrier thicknesses of 1.1nm, 1.4nm and 1.7nm respectively we obtained current densities between 30 and 150kA/cm<sup>2</sup> and peak-to valley-current ratios up to 7:1.The peak voltage is 600mV in the best case and depends on Jp via the voltage drop across the series resistance.

Fig. 3 SEM view of diodes with mesa defined by RIE Fig. 4 Typical I-V at 300K

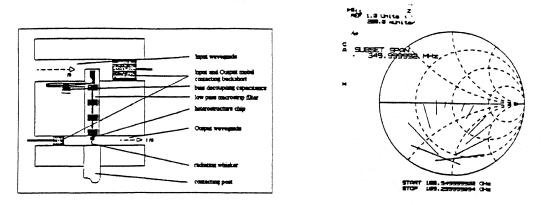

Frequency evaluation: For the rf probing, the thinned samples were inserted into a tripler mount which was designed for harmonic multiplication at sub-millimeter wavelengths. Isolation between the pump and the output frequency and matching at these frequencies are achieved by means of low pass and high pass filters and tuning elements. As seen previously, DBH's exhibit symmetric conductance variations G(-V)=G(V). This property is also verified for the capacitance. This greatly simplify the multiplier design by suppressing the idler at second harmonic. Figure 5 shows a cross section of the tripler mount we have fabricated. This is a cross- guide configuration based on the design of Archer for tripling to 366GHz. The input power is coupled to a microstrip low pass filter on a quartz substrate through a microstrip-waveguide transition. Special attention was paid to these passive elements by measuring the S parameters of low frequency scaled prototypes. For the high pass filter in the output branch we take benefit of the waveguide cutoff frequency (Fc=300GHz). The whisker also plays the role of antenna to couple the third harmonic power generated in the non-linear device to the output. Mobile contacting backshorts are used to match the diode to its embedding.

The effectiveness of the matching was verified by measuring a 2T2 varactor from the University of Virginia. Figure 6 shows the refection coefficient plotted in a Smith chart, measured at the input and by tuning the position of the input backshort. These measurements were carried out at 109GHz with a HP 85109 Network analyzer with a very narrow span of about 350 MHz at a bias of 0.25V. It can be seen that a very good match can be obtained. Confidence in the fact that the input power is effectively coupled to the diode can also be found by biasing the device at the built-in voltage where self-biasing effects can be pointed out.

For the experimental set-up used in harmonic multiplication experiment the source is a carcinotron with an output power up to 200mW between 106 and 123 GHz. A reflectometer allows us to measure the return loss at the input. A corrugated horn radiates the output power which is then focused and filtered by means of quasi-optical lenses and dichroic filters. Power measurements were made using a Golay cell which is very sensitive but measures only relative values. This detector was calibrated at several high power points (~10mW) with an Anritsu bolometer and a Thomas Keating calorimeter. The linear behavior of the Golay cell allows us to extrapolate this calibration to lower power levels and to achieve a sensibility of 100nW at 368GHz.

Fig. 5 Structure of the tripler mount

Fig. 6 Smith chart of S11 for a 2T2

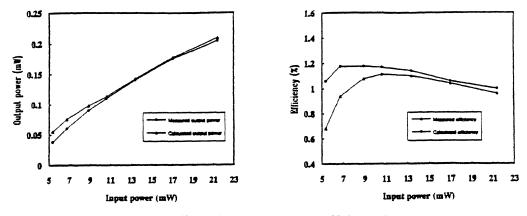

Preliminary rf measurements have been carried out using varactor devices characterized previously at 109 GHz in impedance. The variation of output power and of efficiency as a function of input power we measured at 366GHz are reported in Figure 7. We obtained an output power of about 200 $\mu$ W for an input of 20mW which corresponds to an efficiency of 1%. Also shown are the values of efficiency and of P<sub>out</sub> we have calculated by modeling, by means of the LIBRA design system, the waveguide test fixture and the low frequency section of the rf mount. A good agreement was achieved between measured and simulated data notably by describing the dependence of the efficiency by tuning the backshorts, we finally reached an output power of 800nW at 368GHz for 100mW in input with a device of the 1.4nm run. Under these conditions we measured a return loss of -7dB which means that the power transmitted at the input was 75mW.

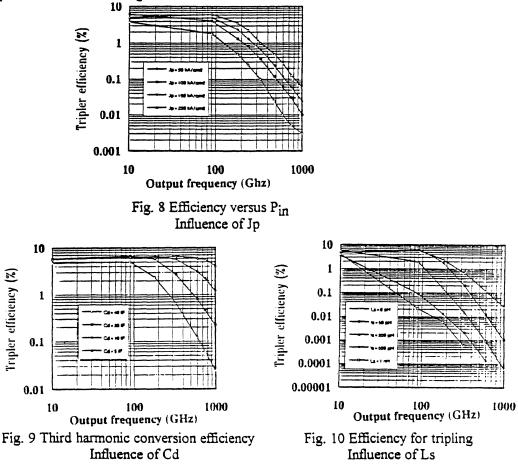

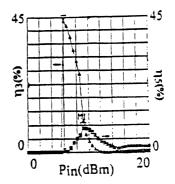

Discussion: Further insight into the power balance can now be obtained by comparing this result with those obtained with conventional varactors despite the fact that DBH's make use of the singularities in the I-V curve whereas varactors work as non linear capacitive elements. The heterostructure has a cutoff frequency fc of around 160GHz. An ideal varactor with a similar fc would give an efficiency of 2. 10<sup>-4</sup>. The Schottky varactor 2T2 with a cut-off frequency of 2THz has a theoretical efficiency of 10%. Its best efficiency measured in our mount was 1%. If we apply the same ratio to the DBH diode we can expect that much higher efficiency can be obtained for samples with much higher current density and hence fc. This increase in the conversion efficiency  $\eta$  as a function of Jp is exemplified in figure 8 which compares  $\eta(f)$  calculated in the framework of harmonic balance simulation by using MDS codes. These results have been computed by means of a fitted form of the I-V characteristics of intraband tunneling structures such as those we fabricated. Four current density values were here considered between 50kA/cm<sup>2</sup> and 250kA/cm<sup>2</sup>. This last value corresponds to the best results achieved up to now with InAs-based resonant tunneling structures such as InGaAs /AlAs double barriers grown on InP. One can note that the frequency capability of devices is dramatically improved at increasing current density notably at submillimeter wavelengths. Also crucial is the intrinsic capacitance of devices as demonstrated in Figure 9 which displays the variations of efficiency as a function of output power for various values of the intrinsic capacitance of devices Cd ranging from 40 fF down to 5 fF. A drastic decrease in efficiency and hence in output power is apparent at high frequencies in particular for devices with Cd of the order of a few tens of femtofarads.

Fig. 7 Output power and efficiency for a 2T2 Comparison between calculated and measured values

Turning now to the influence of the parasitic self inductance due to the interconnecting metallization for a monolithic version or to the whisker for the devices under consideration we obtained the typical evolution  $\eta(f_{out})$  reported in Figure 10. We have considered respectively the ideal case Ls=0, the situation corresponding to integration techniques with air bridged devices we published recently<sup>[4]</sup> where Ls=50pH and several values up to 1nH which are representative of the self inductance due to a whisker. As a general rules huge degradations can be pointed out at increasing Ls values.

Beyond the search of high current density to increase the capability of devices and of low parasitics in the recent context of planar integrated technologies[5], the voltage range for Negative Differential Conductance effects appears also of prime importance. In order to consider this issue, we have compared three kinds of I-V characteristics by computing the variations of efficiency against Pin for frequency tripling and quintupling. Figure 11a shows the results we calculated by means of the large signal MDS simulation program for a resonant tunneling diode with  $\Delta V$ =400mV. As expected, one can observe an abrupt rise in efficiency in the NDC region with a maximum value for  $\eta_3$  of 2.2%. As a consequence despite the presence of a negative differential resistance, we do not exceed the conversion efficiency limit  $\eta_{max} = 1/n^2$  (where n is the harmonic number) found by Page<sup>[6]</sup> for diodes exhibiting a resistive non linearity. On the contrary, when one assumes that the devices exhibit NDC effects over a large  $\Delta V$ , conversion efficiencies are enhanced as seen in Figure 11 b which was computed for  $\Delta V=1V$ . Let us recall that Vp should be as low as possible so that the peak amplitude of the voltage across the diode reaches the voltage corresponding to peak current very rapidly whereas  $\Delta V$  should be increased. One way to enhance  $\Delta V$  is to use extended spacer layers but subsequent amplification affects not only  $\Delta V$  but also Vp.

Fig. 11 (b) Efficiency versus Vrf  $\Delta V=1V$

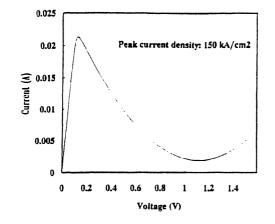

However these shortcomings can be alleviated by taking advantage of interband tunneling phenomena which have been observed for Sb-based material systems. In this case, the conduction (Ec) and valence (Ev) bands can overlap and a high conduction state can be established under forward and reverse conditions near equilibrium. The band offset between Ec and Evistates is typically of a few tens of millielectronvolts and as a consequence the conduction can be stopped very soon with a smooth decrease in the current values which reflects indeed the dispersion curve in the forbidden gap region. At higher voltages, other parasitic conduction mechanisms are involved and the current starts again to increase. Figure 12 gives an example of I-V characteristic which can be expected with these broken gap heterostructures such as InAs/GaSb. The variations are quite similar to those of conventional Esaki diodes except the fact that we do not need a highly doped active region as this is the case for homojunctions. This distinction was early recognized notably by Sollner et al. [7]. The efficiency we calculated with a peak current density of 150kA/cm<sup>2</sup> and Vp=100mV reaches 44% (Figure 13). It is clear that at such theoretical efficiency levels, resonant tunneling diodes are capable of providing adequate power for submillimeter wave applications and to compete with conventional varactors.

Fig. 12 Typical current voltage curve for interband tunneling diodes

Fig. 13 Efficiency against Vrf

Conclusion: High-quality Double Barrier Heterostructures have been successfully fabricated and tested in a frequency conversion with output at submillimeter-wavelengths. Very sensitive power measurements were developed to this aim that permits us to measure an output power of 800nW at 386GHz. These results are discussed in terms of cut-off frequencies showing the requirement of further increase the current density for future improvements in the conversion efficiency and in the operating frequency. On the other hand, heterostructures which involved interband tunneling phenomena appear very promising owing to their current-voltage characteristics more favorable for relaxing the trade-off pointed out for intra-band tunneling structures.

This work was partially supported by the D.R.E.T.(Contract 91.099)

\*O. Tanguy and D. Lippens are with

Institut d'Electronique et de Microélectronique du Nord

Avenue Poincaré, BP 69, 59652 Villeneuve d'Ascq Cedex, France

- **\*\***J. Bruston, J.C. Pernot and G. Beaudin are with

- Ecole Normale Supérieure 24 rue Lhomond 75231 Paris

- Observatoire de Meudon, 5 Place Jules Janssen, 92195 Meudon Cedex, France

- \*\*\*J. Nagle and B. Vinter are with

- Laboratoire Central de Recherches, Thomson CSF

Domaine de Corbeville,91404 Orsay Cedex, France

- <sup>[1]</sup>E. R. Brown, et al ;Appl Phys. Lett; Vol.58, No.20, May 1991, pp2291-2293

- <sup>[2]</sup>R. Bouregba, et al., Electronics Letters, Vol. 26, No. 21, October 1990, pp1804-1805

- <sup>[3]</sup>L. Burgnies, et al., To be published in J. Appl. Phys., May 1994

- <sup>[4]</sup>E. Lheurette, et al., Electronics Letters, Vol. 28, No. 10, May 1992, pp937-338

<sup>[5]</sup>S. T. Allen, et al., IEDM proceedings, 1993, pp407-410

- <sup>[6]</sup>C. H. Page, Proceedings of the IRE, October 1958, pp1738-1740

- <sup>[7]</sup>T.C.L.G. Sollner, et al., Physics of quantum Electron Devices edited by F. Capasso Springer-Verlag