## Monolithic Millimeter-wave and Submillimeter-wave Integrated Circuit (MMIC and S-MMIC) Testing Capabilities at JPL up to 500 GHz

Lorene Samoska, A. K. Fung, Todd C. Gaier, W. R. Deal, V. Radisic, X.B.Mei, and R. Lai Jet Propulsion Laboratory, California Institute of Technology, Pasadena, California 91109 USA

Northrop Grumman Corporation, Redondo Beach, CA USA

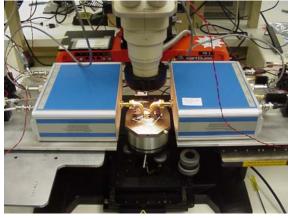

Over the years, our group has been developing on-wafer and waveguide testing capabilities for MMIC amplifiers, oscillators, transistors, and diode circuits up to 500 GHz. In this work, we outline the present state-of-the-art in terms of on-wafer S-parameter measurements, on-wafer noise figure measurements, and on-wafer power measurements up to 350 GHz for a variety of MMIC and new Submillimeter-wave MMIC (S-MMICs) chips. The first S-MMIC chips are described in Reference [1] and were tested at JPL and fabricated at NGST, and include single stage HEMT amplifiers with 2.5 dB of gain at 300 GHz. Figure 1a, below, shows the on-wafer full 2-port vector network analyzer test set used for the measurements up to 325 GHz.

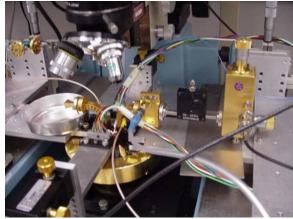

Several years ago we reported the state-of-the-art in HEMT doubler technology up to 320 GHz using on-wafer test equipment outside of its recommended frequency range, which resulted in large uncertainty in measured power data [2]. Today, together with GGB Industries and OML Laboratories, we have developed the submillimeter-wave test sets to measure noise figure and power data to within 1 dB of accuracy on-wafer. Below in Figure 1b is a photograph of our on-wafer noise figure test set, capable of less than +/- 1 dB accuracy up to 270 GHz.

In this work, we will describe the key components required for the measurements, highlight recent test results on MMIC and S-MMIC chips, and plans for future wafer probing up to 500 GHz.

Figure 1a. On-wafer S-parameter test set up to 325 GHz.

Figure 1b. On-wafer noise figure test set at 270 GHz.

[1] "Demonstration of a Sub-MillimeterWave Integrated Circuit (SMMIC) using InP HEMT with a 35-nm Gate," W. R. Deal, S. Din, V. Radisic, J. Padilla, G. Mei, W. Yoshida, P. Liu, J. Uyeda, M. Barsky, T. Gaier, A. Fung, L. Samoska, and R. Lai, 28th IEEE Compound Semiconductor Integrated Circuit Symposium Digest, San Antonio, TX, November, 2006.

[2] "Advanced HEMT MMIC Circuits for Millimeter-wave and Submillimeter-wave Power Sources," Lorene Samoska, Jean Bruston, and Alejandro Peralta, *Proceedings of the Far Infrared, Millimeter, and Submillimeter-wave Detector Workshop*, Monterey, CA, April 1-3<sup>rd</sup>, 2002

This work was carried out in part at the Jet Propulsion Laboratory, California Institute of Technology, under a contract with the National Aeronautics and Space Administration. This work was also supported in part by the DARPA SWIFT Program and Army Research Laboratory under the ARL Contract no. W911QX-06-C-0050.